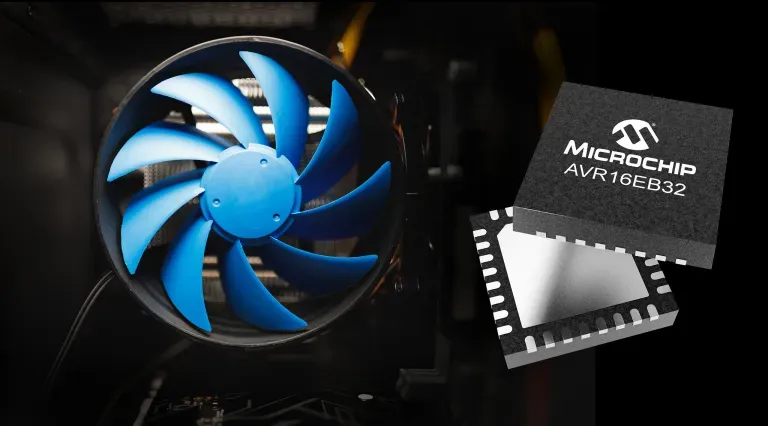

Microchip Technology Inc. has introduced its AVR EB family of microcontrollers (MCUs) that reduces noise, vibration and harshness (NVH) in brushless DC (BLDC) motors, while addressing efficiency and device longevity in a variety of cost-sensitive applications.

Microchip said historically cost-optimized controllers couldn’t deliver these benefits because they required sophisticated control algorithms and waveforms that were outside the capability of these controllers. The new AVR EB MCUs can adjust speed, timing and waveform shape—creating sinusoidal and trapezoidal waveforms—to improve the smoothness of motor operations, reduce noise and increase efficiency at high speeds.

In addition, these adjustments can be made on the fly, with near-zero latency, thanks to on-chip peripherals that enable multiple functions with minimal programming. Benefits include a reduction in code complexity, faster response to changes in operating conditions and lower overall bill of materials cost since several tasks, such as reading environmental sensors and serial communication, can be performed independent of the CPU, Microchip said.

Key features include a new 16-bit timer/counter E (TCE) with four compare channels for pulse-width modulation and waveform extension for BLDC motor control with tunable dead band insertion, a new 24-bit timer/counter F (TCF) for frequency generation and timing and a new programming and debug interface disable for advanced code security. In addition, the devices are housed in a small 3 mm × 3 mm package that can be mounted directly to the motor.

The AVR EB family is supported in Microchip’s MPLAB Development Ecosystem. A new Curiosity Nano Development Board is available for rapid prototyping. The AVR16EB32 Curiosity Nano Evaluation Kit (EV73J36A) connects to MPLAB X, Microchip Studio and IAR Embedded Workbench Integrated Development Environments (IDEs). The MPLAB Code Configurator (MCC) Melody graphical configuration tool also is available to accelerate design development.