Unveiled today at Electronica, AMD designed the new FPGA to act as a “traffic cop” in larger AI systems.Today at Electronica, AMD introduced the Versal Premium Series Gen 2, the industry’s first FPGA platform to support CXL 3.1 and PCIe Gen6.

As AI and data analytics intensify, the infrastructure behind these technologies must keep pace with strenuous data demands. The rise of interconnected systems in data centers has elevated the role of FPGAs in handling complex tasks. With advances in memory scalability and security, AMD has positioned the scalable Versal Premium Series Gen 2 to meet the demands of industries that rely on fast, secure data flow.

All About Circuits spoke with Mike Rather, AMD's senior product line manager, to learn about the new FPGAs firsthand.

Advanced Interconnects

Rather described the Versal Premium Series Gen 2 as a "traffic copy" instead of a primary AI accelerator.

“We’re enabling AI, even though the GPU is the workhorse in this scenario,” he said. “Our role is to manage data movement quickly and efficiently so that GPUs can perform at peak levels.”

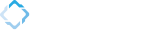

To this end, the Versal Premium Series Gen 2 embraces advanced interconnect technology to meet the high-speed, low-latency data movement between processors and accelerators in AI systems. The solution supports CXL 3.1 and PCIe Gen6, making it the first FPGA to integrate these latest industry standards.

The Versal Premium Gen 2 architecture.

PCIe Gen6 provides a bandwidth of 64 gigabits per second (Gbps) per lane, equating to 2-4x the speed of previous PCIe generations. CXL 3.1, on the other hand, enhances host-to-accelerator connectivity by offering memory coherency and pooling capabilities. CXL allows connected accelerators to share memory directly with the CPU, reducing redundant data movement and latency. By combining PCIe Gen6 and CXL 3.1 support, AMD’s Versal Premium Gen 2 devices achieve a dual eight-lane interface that can support up to 256 Gbps of aggregate bandwidth.

Memory Architecture

AMD has also equipped the Versal Premium Series Gen 2 with a sophisticated memory architecture, including support for LPDDR5X memory at 8,533 megabits per second (Mbps) and DDR5 at 6,400 Mbps. This configuration enables up to 2.7x the memory bandwidth compared to competing devices still operating with DDR4 or LPDDR4 standards.

Expanding CXL in the data center.

This FPGA can also integrate CXL-based memory expansion modules to enhance its memory scalability further. By enabling a multi-host, single-logic-device configuration, the Versal Premium Series Gen 2 can pool and dynamically allocate memory across multiple devices, a feature increasingly demanded in AI applications.

“With CXL memory expansion, we can augment LPDDR5X’s bandwidth by dynamically allocating memory pools across multiple devices,” Rather said. “This architecture supports a multi-headed single logic device (MH-SLD) without needing a switch, ultimately optimizing memory utilization.”

These features are significant for AI applications. CXL memory expansion reduces memory access latency, giving AI cores rapid access to a larger memory pool. At the same time, the high-bandwidth interfaces allow accelerators to process and transmit data more efficiently. Furthermore, AMD's FPGA devices provide DSP engines that can perform mathematical operations required for AI, making them flexible enough to handle some inferencing tasks if needed.

Strengthened Security

With an eye on data security, the Versal Premium Series Gen 2 incorporates a suite of features designed to protect data both in transit and at rest.

Crypto engine block diagram.

It includes integrated PCIe integrity and data encryption (IDE) for secure data transmission, along with inline encryption for DDR memory for end-to-end protection across data flows. AMD has integrated two 400-G, high-speed crypto engines to accelerate encryption and decryption, doubling the throughput over its previous generation. These engines enable data protection at up to 800 Gbps, providing an added layer of security for real-time applications.

Timeline and Development Tools

AMD designed the Versal Premium Series Gen 2 for data centers, aerospace, communications, and test and measurement markets. The company plans to release development tools for the Versal Premium Series Gen 2 in the latter half of 2025, with silicon samples expected by early 2026 and production units by mid-2026.

“If you think about the whole AI era, data is like the crude oil. The more data, the more you can do,” Rather concluded. “That’s really what drives our need for memory and high-speed data transfer, pushing us to innovate on every level of connectivity and processing capability.”